|

高速先生成员--黄刚 一些通用的PCB设计经验以及高速信号理论,都告诉我们PCB上的信号最好都以地平面为参考,尤其是高速走线,建议上下参考平面都是地平面是最好的方法。但是产品类型千千万万,导致叠层的设计也变化万千,有时候为了成本减小层数,这样就可能会导致信号参考到电源平面的情况。当然,作为一名有经验的设计工程师,还是会优先保证主要的高速串行信号上下层都有完整的地平面做参考。在保证重要的高速信号后,一般来说,要去牺牲不那么高速的DDR模块走线了。

没办法,谁叫你速率没有高速信号那么高,关键是你还要用那么多层去布线,所以只能牺牲DDR信号了。那这样就尴尬了,很多PCB工程师觉得违背了他们一贯的设计原则,不敢下手去画了。

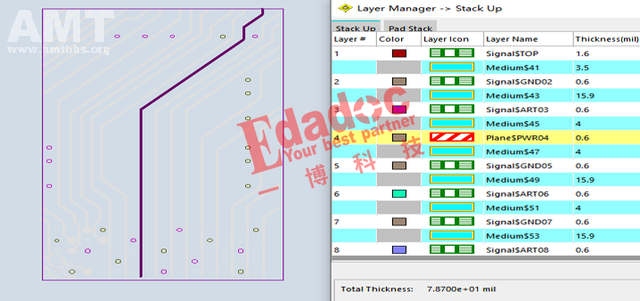

一般这种PCB设计工程师定不了的时候,高速先生就必须出来说话了。我们截取一段DDR的地址信号进行研究,叠层和走线情况如下所示:

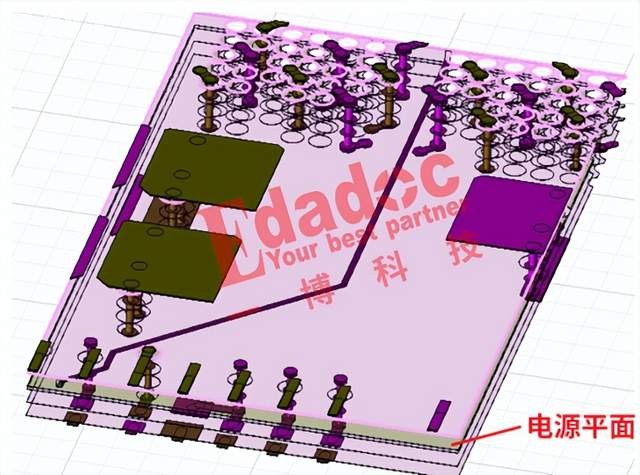

这根地址信号走线在L3层,参考L2和L4层,其中L4层是主要的参考平面,是一个电源平面,距离L3走线层是4mil,L2层虽然是地平面,但是距离L3走线层却有差不多16mil的距离。显而易见,这根L3层的地址信号主要参考的是L4层的电源平面了。就像下面这个3D仿真模型展示的一样。

要不。。。我们还是首先来看看如果是L3层的这根地址信号上下都是地平面的常规情况的结果吧,也就是把上面的电源平面也换成地平面,这样L3层走线上下都是参考地平面了,模型如下所示:

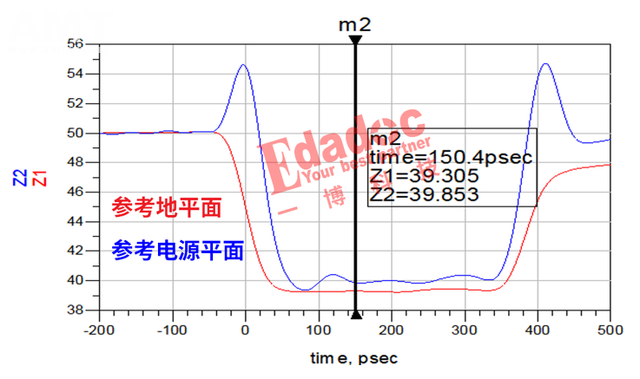

我们先来看看阻抗的情况,这根地址信号的走线是要求按40欧姆来设计,经过仿真后,我们看到上下都是地平面设计的阻抗仿真结果非常接近40欧姆走线阻抗。

那么大家是不是很好奇,如果是参考电源平面的case,阻抗是多少呢?会不会差很远很远啊!淡定,高速先生可以很负责任的告诉大家,不会!如下图所示,参考电源平面后,阻抗也是差不多40欧姆左右。

两者一对比,其实发现,对于阻抗来说,参考电源平面和参考地平面其实差的不远。

那是不是只要阻抗没啥影响,也就代表着DDR信号参考电源平面完整没有问题呢?当然。。。也不是啦!阻抗只是其中的一个性能的表征手段,除此之外,我们还是要关注下插入损耗的情况。 首先,我们还是来看看常规的上下参考地平面的插入损耗结果。和我们预料的一样,参考地平面时,插入损耗的结果从低频一直到高频都是非常线性的,完全没得问题!

这个时候大家是不是很期待,参考电源平面的插入损耗曲线长啥样呢?按道理说,阻抗和参考地平面差别很小,预期插入损耗的结果也不会偏差很大吧?

这次可能又要让大家失望了,参考电源平面的插入损耗结果是下面这个熊样的哦!

啥啊,高频波动那么大,那么差啊,这压根就不行啊!你说对了,高频的确不行,但是别忘了,我们DDR模块的速率,以DDR4为例,一般地址信号的速率也就是1.2Gbps到1.6Gbps,所以理论上我们关注前面3GHz左右的频段就可以了。后面的高频部分都已经是DDR运行频率的3倍频之后了,能量其实就很少了。 咦,如果按照这个观点再对比参考地平面和参考电源平面的插入损耗结果的话,在3GHz以前倒是差得不大哦。这也就是为什么我们的确能看到有的产品的DDR模块的地址控制信号参考电源平面也能跑到额定速率的原因了。。。

当然,上面只是从比较理想的仿真结果上来得出的结论。实际上也要考虑到加工的因素,包括电源平面也会存在噪声影响的因素,还有就是不同设计地址信号走线长度不同,参考的电源网络不同,包括电容配置不同等众多因素。另外为什么在很多非常规设计中,一般只看到地址控制信号参考电源平面的设计,很少看到数据信号参考电源平面呢,那是因为数据信号的速率更高,3倍频下可能就到了5-6GHz以上了,这个时候从上面的插入损耗曲线来看,差异就变得慢慢明显了。总而言之,高速先生的观点是并不完全拒绝DDR走线参考电源平面的可行性,但是遇到这样的非常规设计,我们需要更谨慎的去对待它,最好有一些仿真数据的支撑来确认更大的成功率才行!

问题:大家有没有做过一些觉得是非常规的DDR设计,可以分享下?

关于一博: 一博科技成立于2003年3月,深圳创业板上市公司,股票代码: 301366,专注于高速PCB设计、SI/PI仿真分析等技术服务,并为研发样机及批量生产提供高品质、短交期的PCB制板与PCBA生产服务。致力于打造一流的硬件创新平台,加快电子产品的硬件创新进程,提升产品质量。

版权声明

“特别声明:以上作品内容(包括在内的视频、图片或音频)为用户上传并发布,本平台仅提供信息存储空间服务。

Notice: The content above (including the videos, pictures and audios if any) is uploaded and posted by the user , the platform merely provides information storage space services.”

本文地址: https://www.amtbbs.org/thread-17938-1-1.html

|  |联系我们|法律声明|用户协议|AMT咨询|商务合作|会员入驻|积分充值|积分商城|积分奖励规则|TradEx全球购|加入QQ技术群|添加企业微信|加入微信技术群|智造号|手机版|

世界先进制造技术论坛™(简称AMT™, 智造云™)

( 沪ICP备12020441号-3 )

|联系我们|法律声明|用户协议|AMT咨询|商务合作|会员入驻|积分充值|积分商城|积分奖励规则|TradEx全球购|加入QQ技术群|添加企业微信|加入微信技术群|智造号|手机版|

世界先进制造技术论坛™(简称AMT™, 智造云™)

( 沪ICP备12020441号-3 )